This project is about building a single board 65c02 computer.

It's powered by a WDC 65C02s CPU driven by a 1.8432MHz oscillator clock, with 32KB of SRAM (only 16K used), 32K of ROM, a 65c22 VIA interface, a 6551 ACIA serial interface, and an 20x4 LCD screen.

The ROM is programmed using my self-made EEPROM programmer.

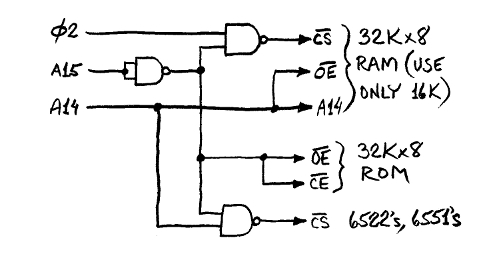

The address decoding logic is following the one described by Garth Wilson in his 6502 Primer, Address decoding page. The corresponding schematics is:

| Address | Component |

|---|---|

$0000-$3FFF |

RAM (16KB) |

$4200-$4203 |

ACIA |

$6000-$600F |

VIA |

$8000-$FFFF |

ROM (32KB) |

At the moment the monitor is very rudimentary, but it serves its purpose.

Monitor will show content at ADDR. You can type:

- a new ADDR (4 char, hex): this will set ADDR to the new value, and display the content. For ex.

04F0 - a value (2 char, hex): this will store the value at ADDR. For ex.

FB 'followed by a char: store the char at ADDR. For ex.'Ajrestore registers to saved values and jump to ADDRccontinue (after a BRK). restore registers to saved values, set ADDR to saved PC (after BRK) and jump to ADDR

Registers manipulation (saved values):

aXX: store XX (hex) in AxXX: store XX (hex) in XyXX: store XX (hex) in YsXX: store XX (hex) in SpXX: store XX (hex) in Pr: print registers value

Early demo of the Monitor in Kowalksi 6502 simulator:

I have implemented my own FORTH kernel for this Homebrew 6502.

Read more here hb6502/forth.

- W65C02S 8–bit Microprocessor

- W65C22S Versatile Interface Adapter (VIA)

- HD44780U LCD Controller/Driver

- UM61256FK-15 32K x 8 Bit SRAM

- AT28C256 32K x8 Paged Parallel EEPROM

- HD44780U LCD Controller/Driver

- SN74HC00 Quadruple 2-Input NAND Gates

- SN74HC138 3-Line To 8-Line Decoders/Demultiplexers

- SN74HC245 Octal Bus Transceivers With 3-State Outputs